三次元プロセッサコア

半導体製造技術の進歩により、近年では積み重なった半導体チップ間で、垂直方向に直接配線することが可能となってきた。プロセッサVLSIの三次元化は、従来の二次元構造に比べて微細化のコスト的な限界を越えてパッケージ容量を増加させるだけでなく、信号転送電力を減らし、実行効率を本質的に向上させる効果が期待されている。

しかし、三次元プロセッサの設計空間は広く、どのようなアーキテクチャやブロック構成が最適か、またどのような配置とすれば効果的かは明らかではない。

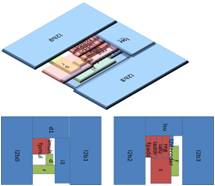

そこで本研究ではSA法により最適な三次元配置を探索するモジュールマッパーを開発し、得られるフロアプランの傾向から三次元化の効果と有効なアーキテクチャの見積もりを進めている。

現在の研究では準最適なTSV位置を軽量に決定する、TSVモジュール手法を提案し、モジュールマッパーに実装した評価を行っている。

- 入江 英嗣,放置 宏佳,眞島 一貴,藤原 大輔,吉見 真聡,吉永 努: 「配線アクティビティを考慮した3次元積層プロセッサ向けフロアプランナー」,情報処理学会論文誌コンピューティングシステム, Vol. 6, No. 3, pp. 131–145, Sep. 2013.