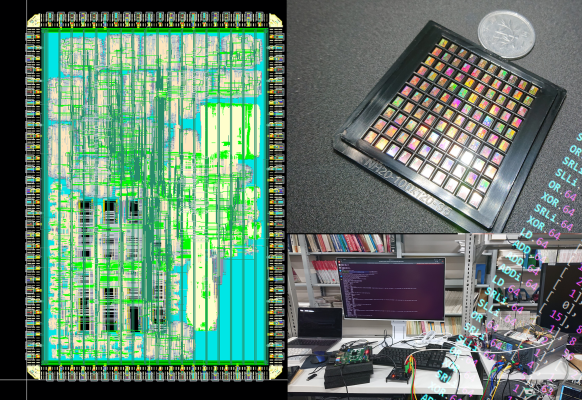

高効率汎用プロセッサ・アーキテクチャ「STRAIGHT」

プロセッサの電力効率や性能を飛躍的に向上させる新しいコンピュータアーキテクチャ「STRAIGHT」の研究を行っています.STRAIGHTは当研究室発のコンピュータアーキテクチャで,従来のRISCコンピュータとは異なり,レジスタ上書きが発生しないという独自の特徴を持つ命令セットです.この性質は,従来作れなかったような高性能コアや高効率コアを実現すると期待されています.研究室では命令セット策定からコンパイラ,マイクロアーキテクチャ,実チップまで総合的に開発を進めており,TSMC28nmプロセスで製作された試作チップで高性能実行を確認しています.現在,更なる高性能化に向けた研究を進める一方で,多くのユーザおよび企業が試用/実用できるように,STRAIGHT基本仕様およびデザインを公開しています.

- 入江 英嗣, 山中 崇弘, 佐保田 誠, 吉見 真聡, 吉永 努: 「もしILPプロセッサのレジスタファイルが分散キーバリューストアになったら」,情報処理学会研究報告, Vol.2013-ARC-206, No. 5, pp. 1–10, Aug., 2013.

- Hidetsugu Irie, Toru Koizumi, Akifumi Fukuda, Seiya Akaki, Satoshi Nakae, Yutaro Bessho, Ryota Shioya, Takahiro Notsu, Katsuhiro Yoda, Teruo Ishihara, Shuichi Sakai: “STRAIGHT: Hazardless Processor Architecture Without Register Renaming”, Int. Symp. on Microarchitecture, pp. 121–133, Oct., 2018.

- Satoshi Mitsuno, Junichiro Kadomoto, Toru Koizumi, Ryota Shioya, Hidetsugu Irie, Shuichi Sakai: “A High-Performance Out-of-Order Soft Processor Without Register Renaming”, Int. Conf. on Field-Programmable Logic and Applications, pp. 73–78, Sep., 2020.

- Toru Koizumi, Shu Sugita, Ryota Shioya, Junichiro Kadomoto, Hidetsugu Irie, Shuichi Sakai: “Compiling and Optimizing Real-world Programs for STRAIGHT ISA”, Int. Conf. on Computer Design, pp. 400–408, Oct., 2021.

- https://github.com/straight-dev/env/

- 杉田 脩, 小泉 透, 塩谷 亮太, 入江 英嗣, 坂井 修一: 「STRAIGHTアーキテクチャにおける効率的なデータフローを実現する命令配置手法」, The 6th cross-disciplinary Workshop on Computing Systems, Infrastructures, and Programming, Jul., 2022. (Best Research Award)