STRAIGHT: Highly Efficient General-purpose Processor Architecture

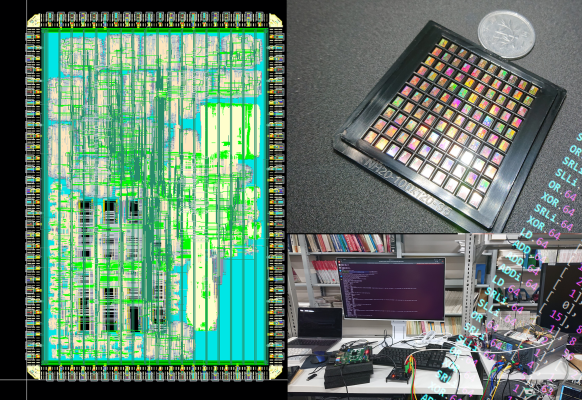

We investigated a novel computer architecture called “STRAIGHT”, which improves the processor efficiency and performance. STRAIGHT is an architecture developed by our team, and unlike conventional RISC computers, it has a unique feature that register overwriting does not occur. This feature is expected to enable high-performance and high-efficiency cores that could not be achieved so far. We have been comprehensively developing the instruction set, compiler, micro-architecture and actual chips and have confirmed high-performance execution on a prototype chip fabricated in TSMC’s 28-nm process. While further research is being conducted to achieve higher performance, the STRAIGHT basic specifications and design are being made publicly available for trial/practical use by many users including industry professionals.

- Hidetsugu IRIE, Daisuke FUJIWARA, Kazuki MAJIMA, and Tsutomu YOSHINAGA: “STRAIGHT: Realizing a Lightweight Large Instruction Window by using Eventually Consistent Distributed Registers”, Int. Workshop on Challenges on Massively Parallel Processors, pp. 336 — 342, Dec., 2012.

- Hidetsugu Irie, Toru Koizumi, Akifumi Fukuda, Seiya Akaki, Satoshi Nakae, Yutaro Bessho, Ryota Shioya, Takahiro Notsu, Katsuhiro Yoda, Teruo Ishihara, Shuichi Sakai: “STRAIGHT: Hazardless Processor Architecture Without Register Renaming”, Int. Symp. on Microarchitecture, pp. 121–133, Oct., 2018.

- Satoshi Mitsuno, Junichiro Kadomoto, Toru Koizumi, Ryota Shioya, Hidetsugu Irie, Shuichi Sakai: “A High-Performance Out-of-Order Soft Processor Without Register Renaming”, Int. Conf. on Field-Programmable Logic and Applications, pp. 73–78, Sep., 2020.

- Toru Koizumi, Shu Sugita, Ryota Shioya, Junichiro Kadomoto, Hidetsugu Irie, Shuichi Sakai: “Compiling and Optimizing Real-world Programs for STRAIGHT ISA”, Int. Conf. on Computer Design, pp. 400–408, Oct., 2021.

- https://github.com/straight-dev/env/