DTB

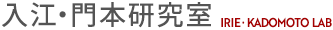

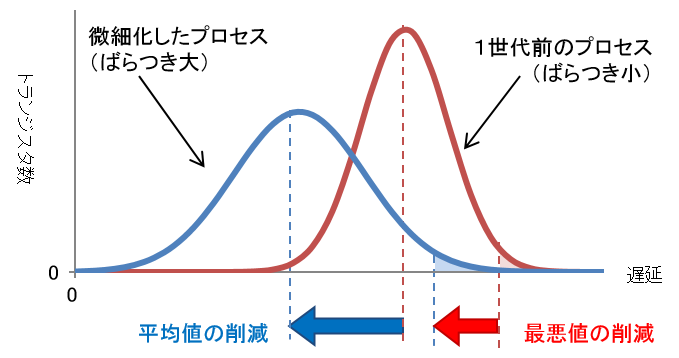

半導体プロセスの微細化に伴い、素子ごとの性能のランダムなバラつきの影響が大きくなっている。素子性能がバラつくと、歩留まりが低下するほか、従来のワースト・ケースに基づいた設計では遅延の見積もりが悲観的になりすぎる。動作時にタイミング故障を検出し回復する機構をVLSIに追加することができれば、プロセス微細化の優位点を最大限に活かした高性能・低電力の動作を得ることができる。

本研究ではタイミング遅れの累積を許容して、エラー回復処理オーバヘッドを削減する動的タイム・ボローイングを提案している。この手法により、従来のタイミング故障検出技術よりもさらに効率的な耐タイミング故障VLSIを実現することができる。本手法は二相ラッチと動的タイミング故障を組み合わせることにより実現する。本手法をクリティカルパスに導入して耐タイミング故障性を得るプロセッサの検証および、クリティカルパスへのラッチ挿入位置設計自動化技術について研究を進めている。

現在は、既存の回路に対して提案手法を適用するプログラムの開発をし、挿入位置を検索するアルゴリズムの実装と評価を行っている。