タイミングに着目したプリフェッチ手法

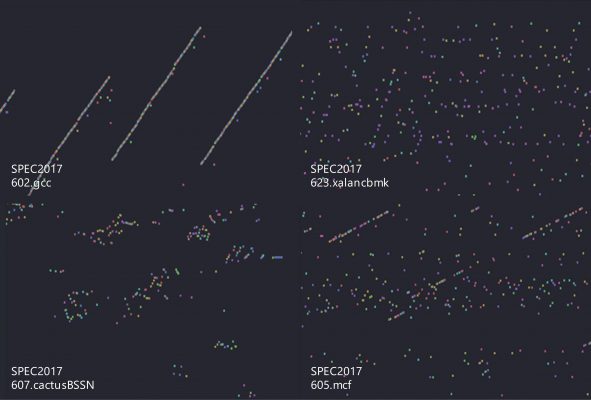

プロセッサの性能を引き出すためには、処理するデータ・命令がキャッシュメモリ上に存在することが重要です。しかし、キャッシュメモリは高速性と引き換えに小容量であるため、データ・命令の一部しか保持することはできません。そこで、将来必要なデータ・命令を予測しキャッシュメモリに移動させる「プリフェッチ」と呼ばれる技法が広く研究されています。既存の研究では、どのデータや命令をプリフェッチすべきかの予測にとどまっていました。これに対し我々は、いつプリフェッチするべきかというタイミングの概念を導入し、適時にプリフェッチを発行することで世界最高性能を達成しました。我々の研究の特色として、sazanami というメモリアクセスパターンの可視化ツールを作成し、研究に活用しています。

- Tomoki Nakamura,Toru Koizumi, Yuya Degawa, Hidetsugu Irie, Suichi Sakai and Ryota Shioya: “T-SKID: Timing Skid Prefetcher”, The Third Data Prefetching Championship (in conjunction with ISCA 2019), June, 2019.

- Tomoki Nakamura, Toru Koizumi, Yuya Degawa, Hidetsugu Irie, Shuichi Sakai, Ryota Shioya, “D-JOLT: Distant Jolt Prefetcher”, The 1st Instruction Prefetching Championship (in conjunction with ISCA 2020), pp. 1–5, June, 2020. (3rd place)

- 中村 朋生, 小泉 透, 出川 祐也, 入江 英嗣, 坂井 修一, 塩谷 亮太: 「プリフェッチ距離の性質に着目した命令プリフェッチャ」, 電子情報通信学会技術研究報告, Vol. 120, No. 121, pp. 1–8, Jul., 2020.(山下記念研究賞, 研究会優秀若手発表賞)

- 小泉 透, 中村 朋生, 出川 祐也, 入江 英嗣, 坂井 修一, 塩谷 亮太: 「アドレスとタイミングの予測を分離したデータプリフェッチャ」, 情報処理学会研究報告, Vol. 2022-ARC-248, No. 17, pp. 1–8, Mar., 2022.

- Toru Koizumi, Tomoki Nakamura, Yuya Degawa, Hidetsugu Irie, Shuichi Sakai, Ryota Shioya: “T-SKID: Predicting When to Prefetch Separately from Address Prediction”, Design, Automation and Test in Europe Conference, pp. 1393–1398, Mar., 2022.